# IE-TFT-020176220-017-06

| 序号 | 内容标题           | 页码   |

|----|----------------|------|

| 1  | 概述             | 2    |

| 2  | 特点             | 2    |

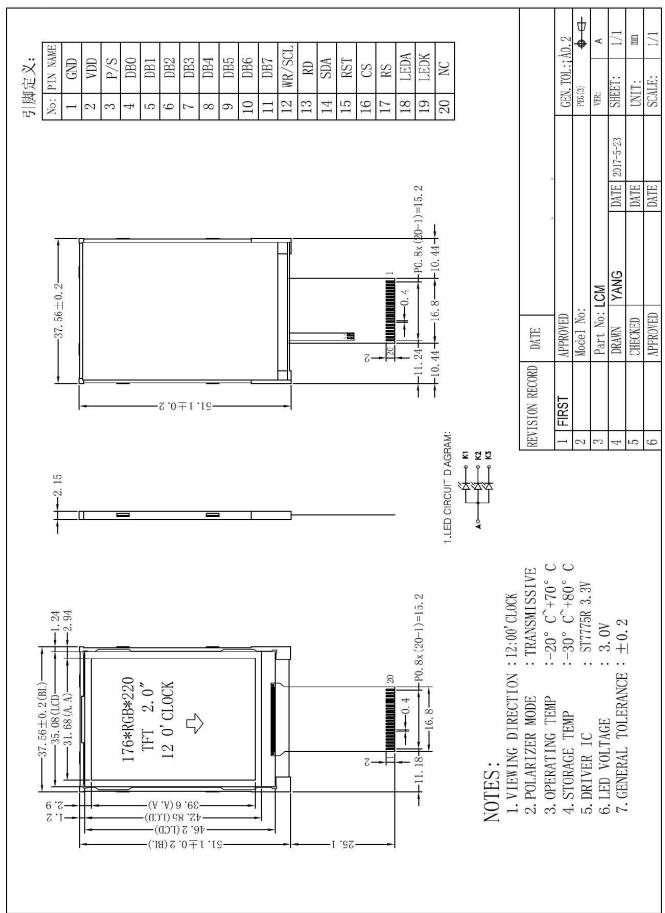

| 3  | 外形及接口引脚功能      | 3~4  |

| 4  | 基本原理           | 4    |

| 5  | 技术参数           | 4~5  |

| 6  | 时序特性           | 5~8  |

| 7  | 指令功能及硬件接口与编程案例 | 9~末页 |

1

### 1概述

晶联讯电子专注于液晶屏及液晶模块的研发、制造。所生产型液晶模块由于使用方便、显示清晰,广泛应用于各种人机交流面板。

JIE-TFT-020176220-017-06可以显示 176 列\*220 行点阵彩色图片。

- **2.** IE-TFT-020176220-017-06

- 2.1结构轻、薄、带背光。

- 2.2 IC 采用 ST7775R, 功能强大, 稳定性好

- 2.3 指令功能强:例如可以用指令控制显示内容顺时针旋转 90、逆时针旋转 90°或倒立竖放。

- 2.4接口方式: 并口、串口。

- 2.5 工作温度宽:-20℃ 70℃;

- 2.6 储存温度宽:-30℃ 80℃;

### 3. 外形尺寸及接口引脚功能

#### 模块的接口引脚功能

| 引线号 | 符号     | 名 称     | 功 能                                |

|-----|--------|---------|------------------------------------|

| 1   | GND    | 接地      | OV                                 |

| 2   | VDD    | 电路电源    | 3. 3V                              |

| 3   | PS     | 串并选择    | 并口接地, <mark>串口接高</mark>            |

| 4   | DB0    | I/0     | 并行数据总线, <mark>串行接口时空</mark>        |

| 5   | DB1    | I/0     | 并行数据总线, <mark>串行接口时空</mark>        |

| 6   | DB2    | I/0     | 并行数据总线, 串行接口时空                     |

| 7   | DB3    | I/0     | 并行数据总线, 串行接口时空                     |

| 8   | DB4    | I/0     | 并行数据总线, <mark>串行接口时空</mark>        |

| 9   | DB5    | I/0     | 并行数据总线, <mark>串行接口时空</mark>        |

| 10  | DB6    | I/0     | 并行数据总线, <mark>串行接口时空</mark>        |

| 11  | DB7    | I/0     | 并行数据总线, 串行接口时空                     |

| 12  | WR/SCL | I/0     | 并口做为 WR 用, <mark>串口做为 SCL 用</mark> |

| 13  | RD     | I/0     | 使能信号                               |

| 14  | SDA    | I/0     | 串行数据(并口时,空)                        |

| 15  | RST    | 复位      | 低电平复位,复位完成后,回到高电平,液晶模块开始工作         |

| 16  | CS     | 片选      | 低电平片选                              |

| 17  | RS     | 寄存器选择信号 | H:数据寄存器 0:指令寄存器 (IC 资料上所写为"A0")    |

| 18  | LDEA   | 背光电源正极  | 背光电源正极,接 3.0V                      |

| 19  | LEDK   | 背光电源负极  | 背光电源负极,接地                          |

| 20  | NC     | 空脚      | 空脚                                 |

表 1:模块的接口引脚功能,详细说明请看  $11 \sim 30$  页

### 4. 基本原理

#### 4.1 背光参数

该型号液晶模块带 LED 背光源。它的性能参数如下:

工作温度:-20∽+70°C; 存储温度:-30∽+80°C;

背光板是白色。

正常工作电流为: 24~60mA (LED 灯数共 3 颗, 每颗灯是 8~20 mA)

工作电压: 3.0V。

### 5. 技术参数

### 5.1 最大极限参数(超过极限参数则会损坏液晶模块)

| 名称   | 符号  |      | 标准值  |      | 单位                     |

|------|-----|------|------|------|------------------------|

|      |     | 最小   | 典型   | 最大   |                        |

| 电路电源 | VDD | -0.3 | 3. 3 | 3. 3 | V                      |

| 工作温度 |     | -20  |      | +70  | $^{\circ}\mathbb{C}$   |

| 储存温度 |     | -30  |      | +80  | $^{\circ}\!\mathbb{C}$ |

表 2: 最大极限参数

### 5.2 直流 (DC) 参数

| 名 称    | 符号   | 测试条件        |     | 标准值  |      | 单位 |

|--------|------|-------------|-----|------|------|----|

|        |      |             | 最小  | 典型值  | 最大   |    |

| 工作电压   | VDD  |             | 2.8 | 3. 0 | 3. 3 | V  |

| 背光工作电压 | VLED |             | 2.9 | 3. 0 | 3. 1 | V  |

| 背光工作电流 | ILED | VLED=3. OV, | 24  | 45   | 60   | mA |

|        |      | 共3颗LED灯并联   |     |      |      |    |

表 3: 直流 (DC) 参数

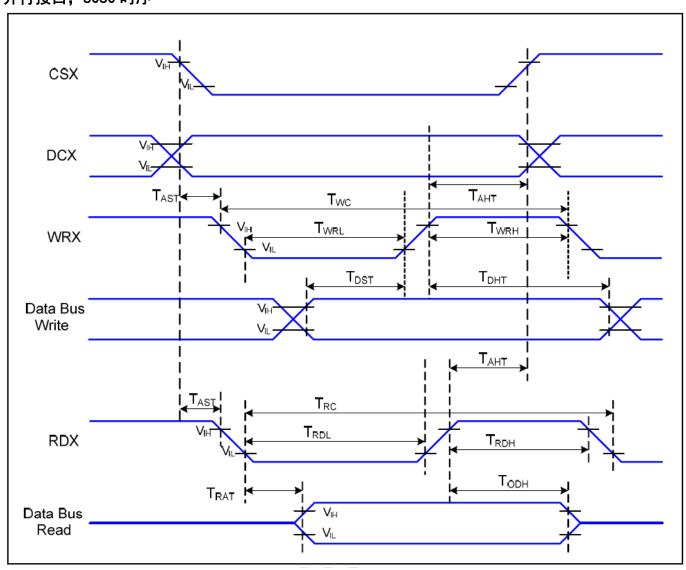

### 6. 读写时序特性

详见 IC 资料 "ST7775R",请找相关客服人员索要。 并行接口,8080 时序

图 2

| Signal   | Symbol | Parameter                       | Min | Max | Unit | Description         |

|----------|--------|---------------------------------|-----|-----|------|---------------------|

| DCX      | TAST   | Address Setup Time              | TBD |     | ns   |                     |

| DCX      | TAHT   | Address Hold Time (Write/Read)  | TBD |     | ns   |                     |

|          | TWC    | Write Cycle                     | TBD |     | ns   |                     |

| WRX      | TWRH   | Control Pulse "H" Duration      | TBD |     | ns   |                     |

|          | TWRL   | Control Pulse "L" Duration      | TBD |     | ns   |                     |

|          | TRC    | Read Cycle (ID)                 | TBD |     | ns   |                     |

| RDX      | TRDH   | Control Pulse "H" Duration (ID) | TBD |     | ns   | When Read ID Data   |

|          | TRDL   | Control Pulse "L" Duration (ID) | TBD |     | ns   |                     |

| DB[17:0] | TDST   | Data Setup Time                 | TBD |     | ns   | TRAT, TRATFM: 3K    |

|          | TDHT   | Data Hold Time                  | TBD |     | ns   | ohm Pull up or Down |

表 4

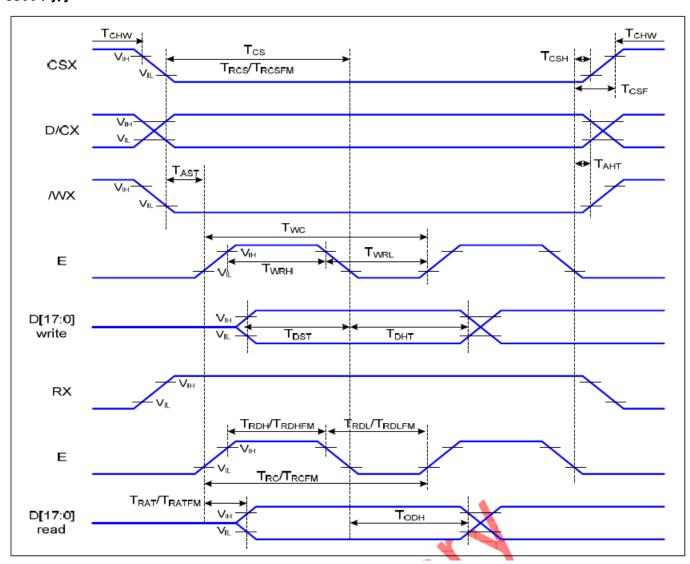

### 6800 时序

| Signal   | Symbol             | Parameter                       | Min | Max | Unit | Description          |

|----------|--------------------|---------------------------------|-----|-----|------|----------------------|

| DCX      | T <sub>AST</sub>   | Address setup time              | TBD |     | ns   |                      |

| DCX      | T <sub>AHT</sub>   | Address hold time (Write/Read)  | TBD |     | ns   | -                    |

|          | T <sub>WC</sub>    | Write cycle                     | TBD |     | ns   |                      |

| Е        | T <sub>WRH</sub>   | Control pulse "H" duration      | TBD |     | ns   |                      |

|          | T <sub>WRL</sub>   | Control pulse "L" duration      | TBD |     | ns   |                      |

|          | T <sub>RC</sub>    | Read cycle (ID)                 | TBD |     | ns   |                      |

| RDX (ID) | T <sub>RDH</sub>   | Control pulse "H" duration (ID) | TBD |     | ns   | When read ID data    |

|          | T <sub>RDL</sub>   | Control pulse "L" duration (ID) | TBD |     | ns   |                      |

| RDX      | T <sub>RCFM</sub>  | Read cycle (FM)                 | TBD |     | ns   | When read from frame |

| (FM)     | T <sub>RDHFM</sub> | Control pulse "H" duration (FM) | TBD |     | ns   |                      |

| (1 101)  | T <sub>RDLFM</sub> | Control pulse "L" duration (FM) | TBD |     | ns   | memory               |

|          | T <sub>DST</sub>   | Data setup time                 | TBD |     | ns   | For maximum          |

| DB[17:0] | T <sub>DHT</sub>   | Data hold time                  | TBD |     | ns   | CL=30pF              |

|          | T <sub>ODH</sub>   | Output disable time             | TBD | TBD | ns   | For minimum CL=8pF   |

表 5

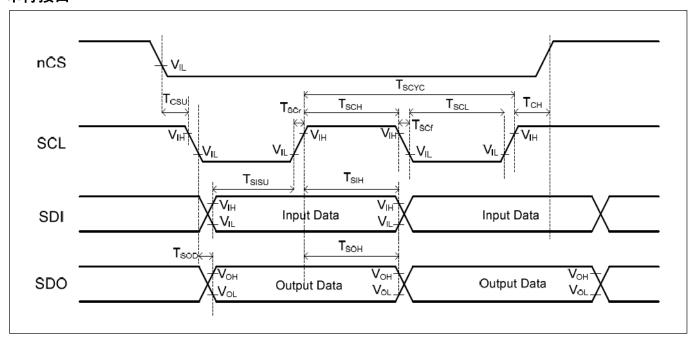

# 串行接口

图 4

| Signal | Symbol     | Parameter                     | Min | Max | Unit    | Description |

|--------|------------|-------------------------------|-----|-----|---------|-------------|

| CSX    | TCSU       | Chip Select Setup Time        | TBD | A   | ns      |             |

| CSA    | TCH        | Chip Select Hold Time         | TBD | •   | ns      | -           |

|        | TSCr ,TSCf | Serial clock rise/fall time   | TBD |     | ns      |             |

|        | TSCH       | SCL "H" pulse width (Write)   | TBD |     | ns      |             |

|        | TSCH       | SCL "H" pulse width (Read)    | TBD |     | ns      |             |

| SCL    | TSCYC      | Serial clock cycle (Write)    | TBD |     | $\mu$ s |             |

|        | TSCYC      | Serial clock cycle (Read)     | TBD |     | $\mu$ s |             |

|        | TSCL       | SCL "L" pulse width (Write)   | TBD |     | ns      |             |

|        | TSCL       | SCL "L" pulse width (Read)    | TBD |     | ns      |             |

| SDI    | TSISU      | Serial Input Data Setup Time  | TBD |     | ns      |             |

| וטפ    | TSIH       | Serial Input Data Hold Time   | TBD |     | ns      |             |

| SDO    | TSOD       | Serial Output Data Setup Time | TBD |     | ns      |             |

| 300    | TSOH       | Serial Output Data Hold Time  | TBD | TBD | ns      |             |

表 6

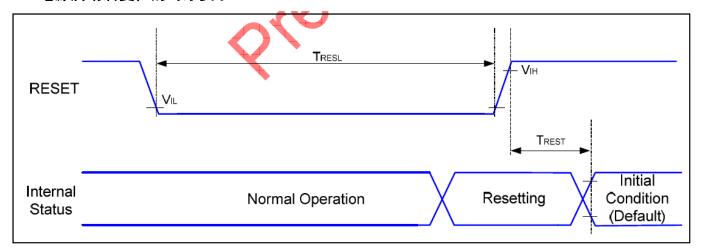

## 6.1 电源启动后复位的时序要求 (RESET CONDITION AFTER POWER UP):

图 5 为电源启动后复位的时序

### 电源启动后复位的时序要求

| Signal | Symbol | Parameter             | Min | Max | Unit | Description |

|--------|--------|-----------------------|-----|-----|------|-------------|

| RESET  | TRESL  | Reset Low Level Width | 1   | -   | ms   |             |

| RESET  | TREST  | Reset Complete Time   | 1   |     | ms   | _           |

# 7. 指令功能:

### 7.1 指令表

### 指 令 表

表8

| No         | Registers                            | W/R | RS | D15  | D14  | D13 | D12   | D11 | D10  | <b>D</b> 9 | D8        | <b>D</b> 7  | D6         | <b>D</b> 5                            | D4   | <b>D</b> 3 | D2   | D1   | D0     |

|------------|--------------------------------------|-----|----|------|------|-----|-------|-----|------|------------|-----------|-------------|------------|---------------------------------------|------|------------|------|------|--------|

| <u>IR</u>  | Index Register                       | W   | 0  | -    | -    | -   | -     | -   | -    | -          | -         | ID7         | ID6        | ID5                                   | ID4  | ID3        | ID2  | ID1  | ID0    |

| <u>00h</u> | Driver Code Read                     | R   | 1  | 0    | 1    | 1   | 1     | 0   | 1    | 1          | 1         | 0           | 1          | 1                                     | 1    | 0          | 1    | 0    | 1      |

| <u>01h</u> | Driver Output Control                | W/R | 1  | VSPL | HSPL | DPL | EPL   | 0   | SM   | GS         | SS        | 0           | 0          | 0                                     | NL4  | NL3        | NL2  | NL1  | NL0    |

| <u>02h</u> | LCD Driving Control                  | W/R | 1  | 0    | 0    | 0   | 0     | 0   | 0    | 0          | INV       | 0           | 0          | 0                                     | 0    | 0          | 0    | 0    | 0      |

| <u>03h</u> | Entry Mode                           | W/R | 1  | 0    | 0    | 0   | BGR   | 0   | 0    | MDT1       | MDT0      | 0           | 0          | I/D1                                  | I/D0 | AM         | 0    | 0    | 0      |

| <u>07h</u> | Display Control 1                    | W/R | 1  | 0    | 0    | 0   | TEMON | 0   | 0    | 0          | 0         | 0           | 0          | 0                                     | GON  | CL         | REV  | D1   | D0     |

| <u>08h</u> | Display control 2                    | W/R | 0  | 0    | 0    | 0   | FP3   | FP2 | FP1  | FP0        | 0         | 0           | 0          | 0                                     | BP3  | BP2        | BP1  | BP0  | 0      |

| 0Bh        | Display Control 4                    | W/R | 1  | 0    | 0    | 0   | 0     | 0   | 0    | 0          | 0         | 0           | 0          | 0                                     | 0    | RTN3       | RTN2 | RTN1 | RTN0   |

| 0Ch        | RGB Display Interface  Control 1     | W/R | 1  | 0    | 0    | 0   | 0     | 0   | 0    | 0          | RM        | 0           | 0          | 0                                     | DM   | 0          | 0    | RIM1 | RIM0   |

| 0Fh        | Frame Marker Position                | W/R | 1  | 0    | 0    | 0   | 0     | 0   | 0    | 0          | 0         | 0           | 0          | 0                                     | 0    | 0          | 0    | 0    | OSC_EN |

| <u>10h</u> | Power Control 1                      | W/R | 1  | 0    | 0    | 0   | 0     | 0   | 0    | 0          | 0         | 0           | 0          | 0                                     | 0    | 0          | 0    | SLP  | STB    |

| <u>11h</u> | Power Control 2                      | W/R | 1  | 0    | 0    | 0   | APON  | 0   | 0    | 0          | 0         | 0           | 0          | 0                                     | 0    | 0          | 0    | 0    | 0      |

| <u>20h</u> | Horizontal DRAM  Address Set         | W/R | 1  | 0    | 0    | 0   | 0     | 0   | 0    | 0          | 0         | AD7         | AD6        | AD5                                   | AD4  | AD3        | AD2  | AD1  | AD0    |

| <u>21h</u> | Vertical DRAM Address<br>Set         | W/R | 1  | 0    | 0    | 0   | 0     | 0   | 0    | 0          | 0         | AD15        | AD14       | AD13                                  | AD12 | AD11       | AD10 | AD9  | AD8    |

| <u>22h</u> | Write Data to GRAM                   | W   | 1  |      |      |     |       |     | DRAN | / Write Da | ata (WD17 | '-0) / Read | l Data (RI | 017-0)                                |      |            |      |      |        |

| <u>22h</u> | Read Data from GRAM                  | R   | 1  |      |      |     |       | -   | 1    | )          |           | 0)771000    | , Data (Na | , , , , , , , , , , , , , , , , , , , |      |            |      |      |        |

| <u>28h</u> | Software Reset                       | W   | 1  | 0    | 0    | 0   | 0     | 0   | 0    | 0          | 0         | 0           | 0          | 0                                     | 0    | 0          | 0    | 0    | 0      |

| <u>30h</u> | Gate Scan Control                    | W/R | 1  | 0    | 0    | 0   | 0     | 0   | 0    | 0          | 0         | 0           | 0          | 0                                     | SCN4 | SCN3       | SCN2 | SCN1 | SCN0   |

| <u>31h</u> | Vertical Scroll Control 1            | W/R | 1  | 0    | 0    | 0   | 0     | 0   | 0    | 0          | 0         | SEA7        | SEA6       | SEA5                                  | SEA4 | SEA3       | SEA2 | SEA1 | SEA0   |

| <u>32h</u> | Vertical Scroll Control 2            | W/R | 1  | 0    | 0    | 0   | ō     | 0   | 0    | 0          | 0         | SSA7        | SSA6       | SSA5                                  | SSA4 | SSA3       | SSA2 | SSA1 | SSA0   |

| <u>33h</u> | Vertical Scroll Control 3            | W/R | 1  | 0    | 0    | 0   | 0     | 0   | 0    | 0          | 0         | SST7        | SST6       | SST5                                  | SST4 | SST3       | SST2 | SST1 | SST0   |

| <u>34h</u> | Partial Driving Control 1            | W/R | 1  | 0    | 0    | 0   | 0     | 0   | 0    | 0          | 0         | SE17        | SE16       | SE15                                  | SE14 | SE13       | SE12 | SE11 | SE10   |

| <u>35h</u> | Partial Driving Control 2            | W/R | 1  | 0    | 0    | 0   | 0     | 0   | 0    | 0          | 0         | SS17        | SS16       | SS15                                  | SS14 | SS13       | SS12 | SS11 | SS10   |

| <u>36h</u> | Horizontal Address End Position      | W/R | 1  | 0    | 0    | 0   | 0     | 0   | 0    | 0          | 0         | HEA7        | HEA6       | HEA5                                  | HEA4 | HEA3       | HEA2 | HEA1 | HEA0   |

| <u>37h</u> | Horizontal Address Start<br>Position | W/R | 1  | 0    | 0    | 0   | 0     | 0   | 0    | 0          | 0         | HSA7        | HSA6       | HSA5                                  | HSA4 | HSA3       | HSA2 | HSA1 | HSA0   |

| <u>38h</u> | Vertical Address End Position        | W/R | 1  | 0    | 0    | 0   | 0     | 0   | 0    | 0          | 0         | VEA7        | VEA6       | VEA5                                  | VEA4 | VEA3       | VEA2 | VEA1 | VEA0   |

| <u>39h</u> | Vertical Address Start  Position | W/R   | 1 | 0 | 0 | 0              | 0              | 0              | 0              | 0              | 0              | VSA7          | VSA6   | VSA5          | VSA4          | VSA3          | VSA2          | VSA1          | VSA0          |

|------------|----------------------------------|-------|---|---|---|----------------|----------------|----------------|----------------|----------------|----------------|---------------|--------|---------------|---------------|---------------|---------------|---------------|---------------|

| <u>50h</u> | Gamma Control 1                  | W/R   | 1 | 0 | 0 | 0              | 0              | 0              | KP1[2]         | KP1[1]         | KP1[0]         | 0             | 0      | 0             | 0             | 0             | KP0[2]        | KP0[1]        | KP0[0]        |

| <u>51h</u> | Gamma Control 2                  | W/R   | 1 | 0 | 0 | 0              | 0              | KP3[3]         | KP3[2]         | KP3[1]         | KP3[0]         | 0             | 0      | 0             | 0             | KP2[3]        | KP2[2]        | KP2[1]        | KP2[0]        |

| <u>52h</u> | Gamma Control 3                  | W/R   | 1 | 0 | 0 | 0              | 0              | 0              | KP5[2]         | KP5[1]         | KP5[0]         | 0             | 0      | 0             | 0             | KP4[3]        | KP4[2]        | KP4[1]        | KP4[0]        |

| 53h        | Gamma Control 4                  | W/R   | 1 | 0 | 0 | SELV63         | SELV63         | SELV63         | SELV62         | SELV62         | SELV62         | SELV1         | SELV1  | SELV1         | SELV1         | SELV0         | SELV0         | SELV0         | SELV0         |

| 3311       | Garrina Control 4                | VV/IX | - | O | U | P[2]           | P[1]           | P[0]           | P[2]           | P[1]           | P[0]           | P[3]          | P[2]   | P[1]          | P[0]          | P[3]          | P[2]          | P[1]          | P[0]          |

| <u>54h</u> | Gamma Control 5                  | W/R   | 1 | 0 | 0 | 0              | 0              | VOS0<br>P[3]   | VOS0<br>P[2]   | VOS0<br>P[1]   | VOS0<br>P[0]   | 0             | 0      | 0             | 0             | VRF0<br>P[3]  | VRF0<br>P[2]  | VRF0<br>P[1]  | VRF0<br>P[0]  |

| <u>55h</u> | Gamma Control 6                  | W/R   | 1 | 0 | 0 | 0              | 0              | 0              | KN1[2]         | KN1[1]         | KN1[0]         | 0             | 0      | 0             | 0             | 0             | KN0[2]        | KN0[1]        | KN0[0]        |

| <u>56h</u> | Gamma Control 7                  | W/R   | 1 | 0 | 0 | 0              | 0              | KN3[3]         | KN3[2]         | KN3[1]         | KN3[0]         | 0             | 0      | 0             | 0             | KN2[3]        | KN2[2]        | KN2[1]        | KN2[0]        |

| <u>57h</u> | Gamma Control 8                  | W/R   | 1 | 0 | 0 | 0              | 0              | 0              | KN5[2]         | KN5[1]         | KN5[0]         | 0             | 0      | 0             | 0             | KN4[3]        | PKN4[2]       | KN4[1]        | KN4[0]        |

| <u>58h</u> | Gamma Control 9                  | W/R   | 1 | 0 | 0 | SELV63<br>N[2] | SELV63<br>N[1] | SELV63<br>N[0] | SELV62<br>N[2] | SELV62<br>N[1] | SELV62<br>N[0] | SELV1<br>N[3] | SELV1  | SELV1<br>N[1] | SELV1         | SELV0<br>N[3] | SELV0<br>N[2] | SELV0<br>N[1] | SELV0<br>N[0] |

| <u>59h</u> | Gamma Control 10                 | W/R   | 1 | 0 | 0 | 0              | 0              | VOS0<br>N[3]   | VOS0<br>N[2]   | VOS0<br>N[1]   | VOS0<br>N[0]   | 0             | 0      | 0             | 0             | VRF0<br>N[3]  | VRF0<br>N[2]  | VRF0<br>N[1]  | VRF0<br>N[0]  |

| <u>65h</u> | ID code                          | R     |   | 0 | 0 | 0              | 0              | 0              | 0              | 0              | 0              | 0             | 0      | 0             | 0             | ID3           | ID2           | ID1           | ID0           |

| <u>66h</u> | SPI Read/Write Control           | W/R   | 1 | 0 | 0 | 0              | 0              | 0              | 0              | 0              | 0              | 0             | 0      | 0             | 0             | 0             | 0             | 0             | R/WX          |

| B0h        | Power Control 3                  | W/R   | 1 | 0 | 0 | VCM5           | VCM4           | VCM3           | VCM2           | VCM1           | VCM0           | 0             | 0      | VGLSEL<br>1   | VGLSEL<br>0   | 0             | 0             | VGHBT1        | VGHBT0        |

| <u>B1h</u> | Power Control 4                  | W/R   | 1 | 0 | 0 | 0              | VRHN4          | VRHN3          | VRHN2          | VRHN1          | VRHN0          | 0             | 0      | 0             | VRHP4         | VRHP3         | VRHP2         | VRHP1         | VRHP0         |

| B2h        | Power Control 5                  | W/R   | 1 | 0 | 0 | 0              | 0              | 0              | AVCLS2         | AVCLS1         | AVCLS0         | 0             | 0      | BCLK_DI<br>V1 | BCLK_DI<br>V0 | 0             | AVDDS2        | AVDDS1        | AVDDS0        |

| D2h        | NVM ID Code                      | W/R   | 1 | 0 | 0 | 0              | 0              | 0              | 9              | 0              | 0              | 0             | 0      | 0             | 0             | ID3           | ID2           | ID1           | ID0           |

| <u>D9h</u> | NVM Control Status               | W/R   | 1 | 0 | 0 | 0              | 9              | 0              | 0              | 0              | 0              | 0             | VMF_EN | 0             | 0             | 0             | 0             | 0             | 0             |

| DFh        | NVM Write Command                | W     | 1 | 0 | 0 | 0              | 0              | 0              | 0              | 0              | 0              | 1             | 0      | 1             | 0             | 0             | 1             | 0             | 1             |

| FAh        | NVM Enable                       | W/R   | 1 | 0 | 0 | 0              | O              | 0              | 0              | 0              | 0              | PROG<br>_MODE | 0      | 0             | 0             | 0             | 1             | MTP<br>_PROG  | 0             |

| FEh        | NVM VCOM Offset                  | W/R   | 1 | 0 | 0 | 0              | 0              | 0              | 0              | 0              | 0              | 1             | 0      | 0             | VMF4          | VMF3          | VMF2          | VMF1          | VMF0          |

| <u>FFh</u> | NVM Command Enable               | w     | 1 | 0 | 0 | 0              | 0              | 0              | 0              | 0              | 0              | 0             | 0      | 0             | 0             | 0             | 0             | CMD1_<br>EN   | CMD2_<br>EN   |

### 7.2 初始化方法

用户所编的显示程序, 开始必须进行初始化, 否则模块无法正常显示, 过程请参考程序

#### 点亮液晶模块的步骤

#### 硬件准备:

开发板(或专门设计的主板)、单片机、电源、连接线、仿真器或程序下载器(又名烧录器)

### 正确地接线

根据说明书正确地与开发板连接,连接的线包括:液晶模块电源线、背光电源线、10端口(接口) 10端口包括:并口时:CS、RESET 、RW、E、RS、DO--D7,串口时: CS、SCLK、SDA、RESET、RS

### 编写软件

背光给合适的直流电可以点亮,但液晶 屏里面没有程序,只给电不能让液晶屏 显示(我们通常说"点亮"),程序须 另外编写,并烧录(下载)到单片机里 液晶模块才能工作。

### 7.3 程序举例:

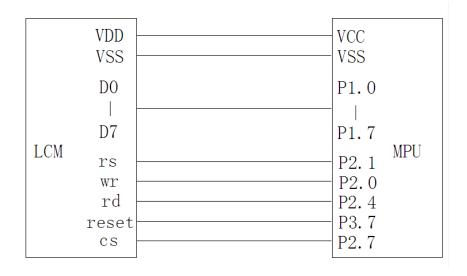

液晶模块与 MPU(以 8051 系列单片机为例)接口图如下:并行接口

| 20PIN                                             |                                                                          |                   |

|---------------------------------------------------|--------------------------------------------------------------------------|-------------------|

| GND VDD PS DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 WR/SCL | 1 VSS 2 3.3V 3 VSS 4 D0 5 D1 6 D2 7 D3 8 D4 9 D5 10 D6 11 D7 12 WR 13 RD |                   |

| RD SDA RST CS RS LEDA LEDK NC                     | 14<br>15 RST<br>16 CS<br>17 RS<br>18 A<br>19 VSS<br>20                   | R1<br>3.3V<br>10欧 |

| L<br>C<br>M | VSS<br>VDD<br>RS<br>RST<br>CS<br>SCK<br>SDA |  | VSS(OV)<br>VDD(3.3V)<br>P1.1<br>P3.1<br>P3.0<br>P3.2<br>P1.0 | MCU |

|-------------|---------------------------------------------|--|--------------------------------------------------------------|-----|

|-------------|---------------------------------------------|--|--------------------------------------------------------------|-----|

| 20PIN        |          |         |

|--------------|----------|---------|

| GND          | 1 VSS    |         |

| VDD          | 2 3.3V   |         |

| PS           | 3 3.3V   |         |

| DB0          | 4        |         |

| DB1          | <u>5</u> |         |

| DB2          | 7        |         |

| DB3          | 8        |         |

| DB4          | 9        |         |

| DB5          | 10       |         |

| DB6          | 11       |         |

| DB7          | 12 SCK   |         |

| WR/SCL<br>RD | 13       |         |

| SDA          | 14 SDA   |         |

| RST          | 15 RST   |         |

| CS           | 16 CS    | R1 2.2V |

| RS           | 17 RS    | 3.3V    |

| LEDA         | 18 A     | 10欧     |

| LEDK         | 19 VSS   |         |

| NC           | 20       |         |

|              |          |         |